FPGA Design solution

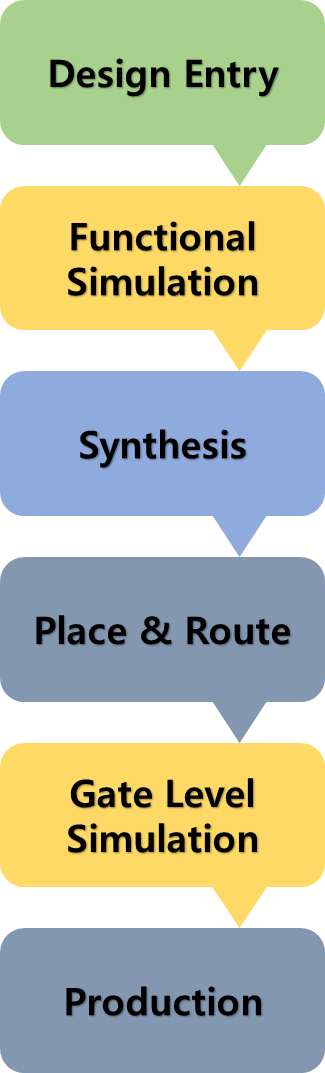

FPGA Design Flow

FPGA Design Flow 는 Design Entry > Functional Simulation > Synthesis > Place & Route > Gate Level Simulation > Production 의 절차로 진행됩니다. FPGA 개발 시 Design Flow 에 맞추어 각 단계를 수행하고 검증해야 합니다. 전반적으로 Design Flow 를 따르지만, 프로세스에 특정단계를 추가할 수 있습니다.

EDMFG 에서는 FPGA 를 개발 하는데 필요한 솔루션에 대해서 컨설팅, 제품 공급 및 지원을 하고 있습니다. 개발자의 개발 환경에 맞추어 가장 적합한 솔루션을 제공합니다.

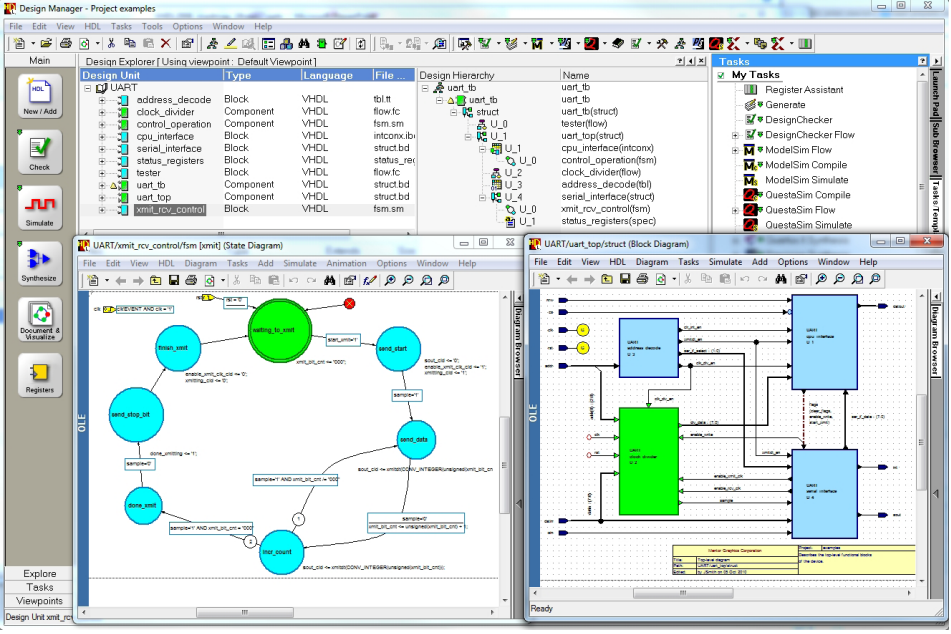

Design Entry

복잡한 FPGA 및 ASIC을 설계하기위한 새로운 접근법을 제공하는 강력한 HDL 기반 환경입니다. 엔지니어 및 엔지니어링 팀에서 사용되며 설계를 분석, 작성 및 관리하는 데 사용되는 강력한 HDL 기반 환경입니다.

제품 특징

- Graphic 및 Text 기반의 설계 방식

- 사용자 Rule 에 따라 자동으로 RTL 품질 검사

- 버전 관리 가능

- IP Reuse 를 위한 디자인 퀄리티 확인

- 업스트림 및 다운스트림 Tool 및 프로세스를 위한 유연한 환경 제공

- 시각화 및 HTML 스냅 샷을 사용하여 쉽고 빠르게 문서화

제품 특징

- Graphic 및 Text 기반의 설계 방식

- 사용자 Rule 에 따라 자동으로 RTL 품질 검사

- 버전 관리 가능

- IP Reuse 를 위한 디자인 퀄리티 확인

- 업스트림 및 다운스트림 Tool 및 프로세스를 위한 유연한 환경 제공

- 시각화 및 HTML 스냅 샷을 사용하여 쉽고 빠르게 문서화

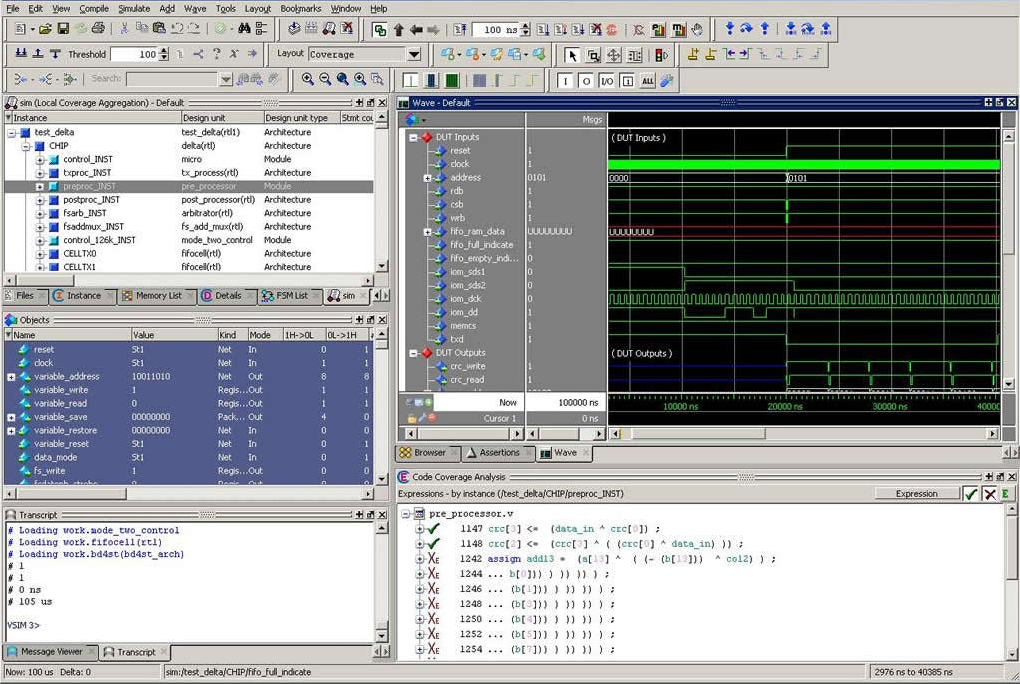

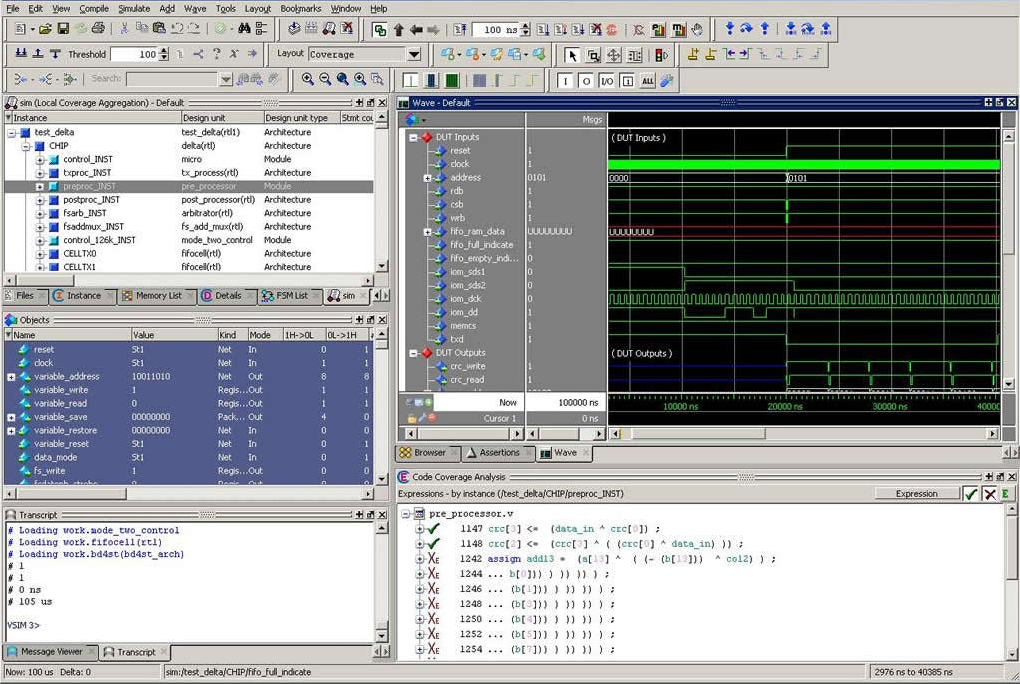

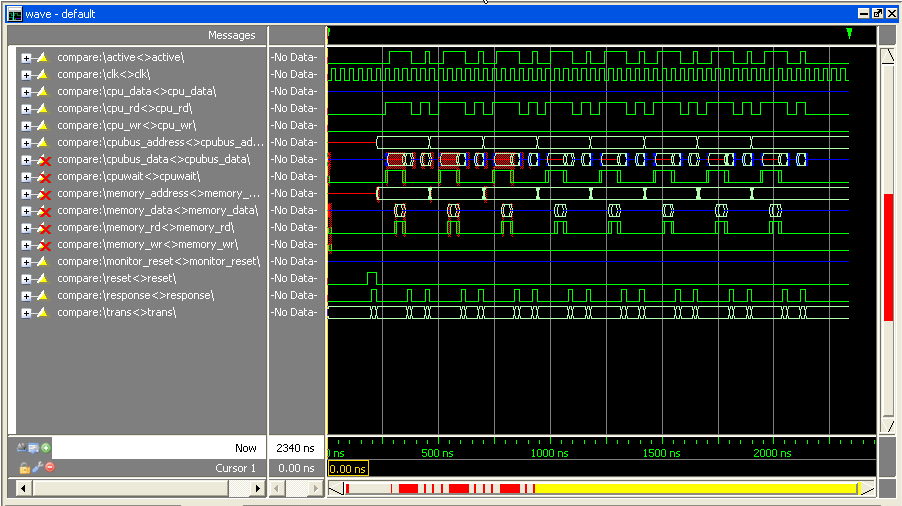

Functional Simulation

고성능 시뮬레이션과 Verilog, SystemVerilog, VHDL, SystemC, SVA, UPF 및 UVM의 가장 완벽한 지원을 위한 통합 고급 검증 솔루션을 제공하며, 복잡한 FPGA 및 SoC 설계 검증의 위험을 줄일 수 있는 포괄적인 검증 플랫폼입니다.

제품 특징

- VHDL, Verilog, SystemC, SystemVerilog 등 언어에 상관없이 동일한 GUI 를 통해 개발 및 디버깅

- Mixed Design Simulation 및 Verification 환경 제공

- Interactive 그래픽 요소(Windows, Toolbars, Menus 등)가 종합적으로 배치

- Code Coverage 기능을 지원하여 다양한 Coverage Metric 기반으로 결과를 출력

제품 특징

- VHDL, Verilog, SystemC, SystemVerilog 등 언어에 상관없이 동일한 GUI 를 통해 개발 및 디버깅

- Mixed Design Simulation 및 Verification 환경 제공

- Interactive 그래픽 요소(Windows, Toolbars, Menus 등)가 종합적으로 배치

- Code Coverage 기능을 지원하여 다양한 Coverage Metric 기반으로 결과를 출력

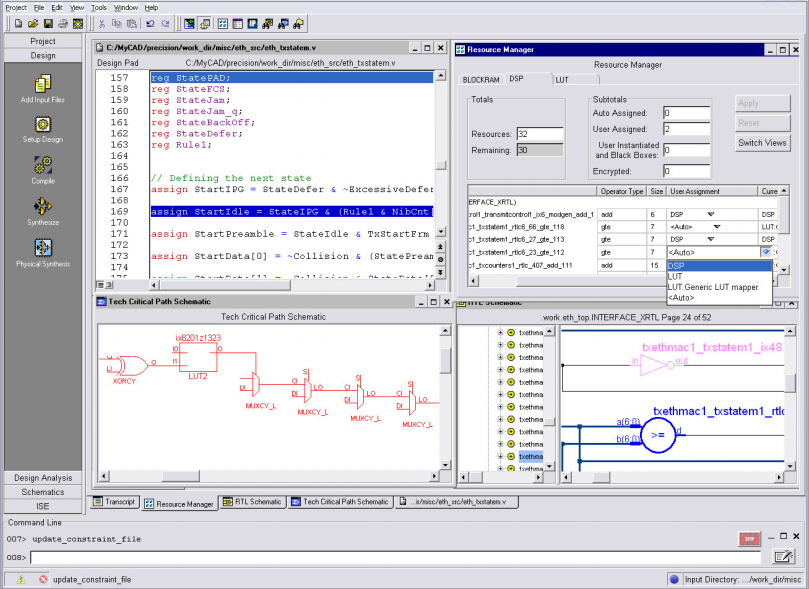

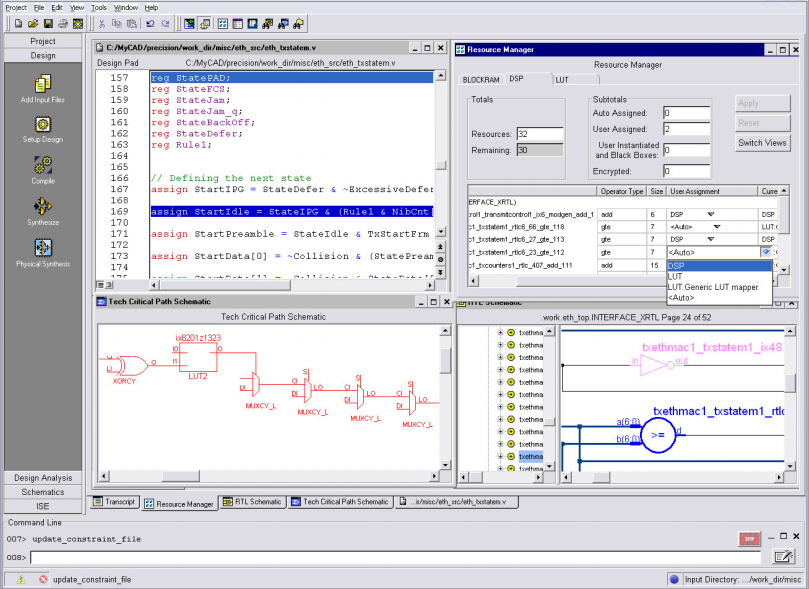

Synthesis

우수한 품질의 결과와 포괄적인 FPGA 벤더 독립적 솔루션의 일부를 제공하는FPGA 합성 솔루션입니다. 고품질의 결과를 제공하고 산업별 요구 사항을 제공함으로써 상업용 애플리케이션과 Mil-aero 및 safety-critical systems 에 이점을 제공합니다.

제품 특징

- 모든 Ventor 의 FPGA 합성을 지원

- 높은 퀄리티의 결과물

- Verilog, VHDL, SystemVerilog 및 EDIF 형식의 모든 조합 지원

- ASIC 프로토 타이핑 지원

제품 특징

- 모든 Ventor 의 FPGA 합성을 지원

- 높은 퀄리티의 결과물

- Verilog, VHDL, SystemVerilog 및 EDIF 형식의 모든 조합 지원

- ASIC 프로토 타이핑 지원

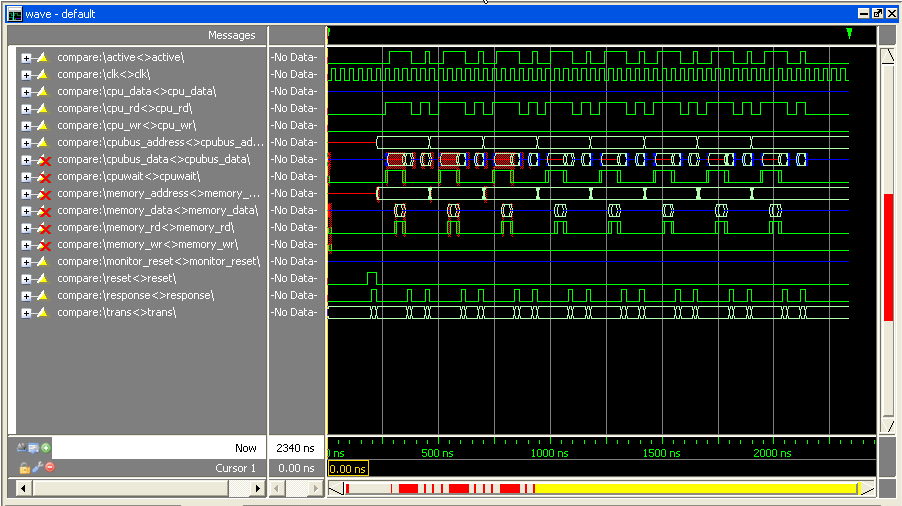

Gate Level Simulation

합성과 P&R 이후의 결과물인 Netlist 파일을 이용하여, 모든 Delay 값을 적용하여 Full timing Simulation 을 진행하여, RTL 레벨에서의 Simulation 결과와 동일한 Out Put 이 발생하는지 체크합니다

제품 특징

- 두 개의 시뮬레이션 출력 비교

- Wizard 를 통한 간편한 사용 방법

- 차이점에 대한 하이라이트

- 강력한 검색 옵션

- Text Report 제공

제품 특징

- 두 개의 시뮬레이션 출력 비교

- Wizard 를 통한 간편한 사용 방법

- 차이점에 대한 하이라이트

- 강력한 검색 옵션

- Text Report 제공